Новини України

Підбірка новин з українських джерел

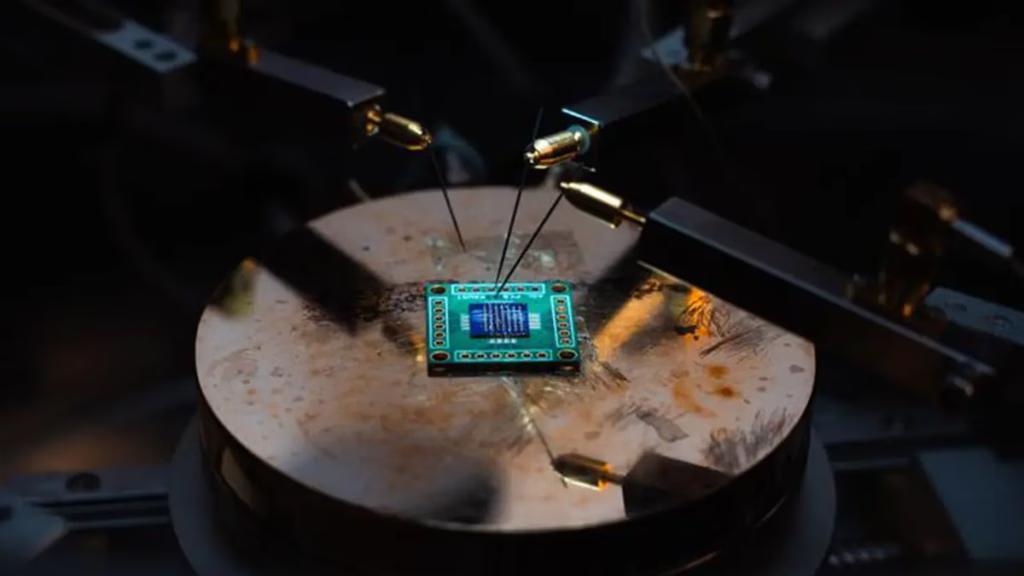

Вчені створили перший у світі шестишаровий гібридний мікрочип

Перший у світі шестишаровий гібридний CMOS-чіп прокладає шлях для надтонкої, гнучкої та ефективної електроніки. Угонці за зменшення розмірів, швидшість та ефективність електроніки вчені з Університету науки і технологій короля Абдалли (KAUST) у Саудівській Аравії досягли прориву, який може змінити майбутнє мікрочипів.

Вони створили перший у світі гібридний шестишаровий КМОП-мікрочип, призначений для електроніки великої площі. Досі гібридні чіпи з вертикальним укладанням обмежувалися двома шарами. Цей прогрес значно перевищує можливості, які були можливі раніше.

«У розробці мікрочіпів головне — це упакувати більше потужності в меншому просторі. Удосконалюючи кілька етапів виготовлення, ми пропонуємо план вертикального масштабування та збільшення функціональної щільності далеко за межі сьогоднішніх можливостей», — сказав Сараванан Ювараджа, провідний дослідник і постдок KAUST.

За словами дослідників, це більше, ніж просто технічний подвиг, оскільки це вказує на нову архітектуру для інтелектуальних електронних пристроїв, носимих пристроїв та медичних виробів.

Хитрощі для вийти за рамки двох стеків

Протягом десятиліть напівпровідникова промисловість покладалася на просте правило — зменшити розмір транзистора, щоб розмістити більше його на плоскій поверхні. Однак ця стратегія зараз стикається з труднощами, оскільки транзистори стають надзвичайно малими, квантові ефекти та зростання виробничих витрат роблять подальшу мініатюризацію практично неможливою.

Дослідники вважають, що рішення полягає не в зменшенні розмірів, а у вертикальному переході, тобто укладанні схем шар за шаром, як у хмарочосі, але це пов’язано з серйозними труднощами.

Наприклад, традиційне виробництво мікросхем вимагає високих температур, які можуть пошкодити нижні шари, а вирівнювання кількох шарів з ідеальною точністю є надзвичайно складним. Досі ці перешкоди обмежували кількість шарів, які можна безпечно та ефективно укладати один в одного.

Щоб подолати такі труднощі, дослідники переосмислили принцип створення мікрочипів з нуля. Замість того щоб покладатися на високотемпературне виробництво, вони розробили процес, у якому жоден крок не перевищував 302 градуси за Фаренгейтом (150 градусів Цельсія), при цьому більша частина роботи виконувалася за температури, близької до кімнатної.

Такий підхід запобіг пошкодженню нижніх шарів під час додавання нових. Кожен шар чіпа містить крихітні транзистори, які обробляють електричні сигнали. Деякі з них виготовлені з неорганічних матеріалів (оксид індію n-типу), а інші — з органічних сполук.

Ці взаємодоповнюючі матеріали, об’єднані в єдину структуру, створюють те, що відомо як гібридна CMOS-архітектура, яка є основою більшості електронних пристроїв. Крім того, команда також удосконалила підготовку та з’єднання кожної поверхні. Забезпечуючи гладкість та точне вирівнювання інтерфейсів, вони забезпечили ефективний потік електричних сигналів між шарами.

Кінцевим результатом став чіп із шістьма активними шарами — утричі більше, ніж будь-який гібридний КМОП-чіп, створений раніше. Він продемонстрував стабільну роботу та енергоефективні логічні схеми, довівши, що вертикальне укладання може забезпечити вищу продуктивність без перегріву чи електричних перешкод. Дослідження опубліковане в Nature Electronics.